# **High Speed & Low Power Comparator Designs for Flash ADC**

# [1]E.Chandrasekhar, [2] K. Ramanjaneyulu

[1]Department of ECE, Chaitanya Bharathi Institute of Technology (CBIT), Hyderabad, [2]Department of ECE, PVP Siddhartha Institute of Technology (PVPSIT), Vijayawada,

**ABSTRACT:** In this paper the design of low power arm latch comparator for 4 bit flash ADC was presented. The 4 bit Flash ADC required 15(2<sup>N-1</sup>) comparators and a thermometer code word to binary code encoder. The major issue in the design of Flash ADC is the large power consumption because of the large number of comparators used in it. So in order to reduce the power consumption of a Flash ADC, we have design a comparator with very low power consumption. Different comparators are designed and their power consumptions are observed. The comparator with lowest power consumption is selected. All comparators are designed and simulated in CMOS 180nm and 45nm technology. The schematic of the all circuits are design with cadence virtuoso.

**Index Terms**—Cadence virtuoso, CMOStechnology, Flash ADC, latch comparator and low power consumption

## I. INTRODUCTION

An Analog to Digital Convertor (ADC) is a device which converts the analog input to the digital output. Among all the ADC's we have Flash ADC is the fastest ADC which samples the given analog voltage in a single clock pulse.

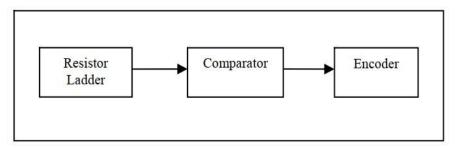

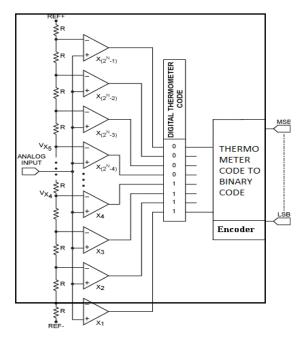

The block diagram of Flash ADC is shown in below figure 1.1. The circuit diagram of N-bit Flash ADC is shown in figure 1.2 which as 2N-1 comparators arranged in sequentially.

Fig. 1.1 General Block Diagram of ADC

A comparator design is more important when you design flash ADC. Because it consumes more power in the whole design and there are 2N-1 comparators which consumes lot of power [1]. In the Section II we proposed different types of comparator designs. The one which consumes low power is selected for ADC design.

The comparator is also called as 1-bit ADC and it is one of the most important block in ADCs. The basic configuration of the comparator can be one of the three types, namely (i) Simple inverter, (ii) Operational amplifier (in open loop configuration), and (iii) Differential amplifier along with cross – coupled latch. Op-amp is the most widely used component in

<sup>[1]</sup>chandrasekhar404@gmail.com, [2]kongara.raman@gmail.com

electronics and normally usedwith negative feedback. It can also be used as comparator in open loop configuration.

In the analog-to-digital conversion, the input is sampled in first step and applied to the combination of comparator to determine the digital output of analog input.

Fig. 1.2 N-Bit Flash ADC

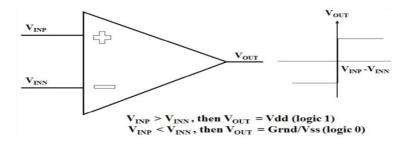

The conversion speed of these comparators is restricted by the decision making responsetime of it. The basic application of a CMOS comparator is to find out whether a given signal is greater or smaller than the reference signal. The schematic symbol of a comparator is depicted in Fig. 1.3.

The comparator can be thought of as a decision-making circuit. If VINP (V+ or VP) input of the comparator is at a greater potential than VINN (V- or Vn) input, the output of the comparator is at Vdd (High or Logic 1), whereas if VINP input is at a potential less than VINN input, output of the comparator is at Vss (Low or Logic 0).

Fig.1.3. Schematic of Comparator

#### II. COMPARATOR

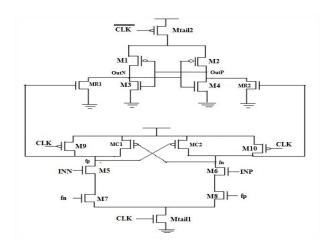

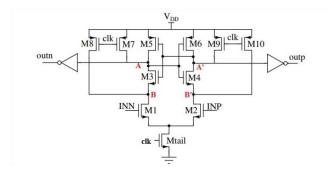

#### A. Conventional Dynamic Comparator

Comparator is the major block of the Flash ADC. Inputs are connected to the inverter and non-inverting terminals will gives the output either logic high or low. In this design, the

input is given to the non inverting terminal of the comparator and reference voltage is given to the inverting terminal of the comparator. There are different types of comparator designs. In this paper we have define three designs. Below figure shows the conventional comparator design.

The design is having clocked regenerative latch formed with the two inverters connected cross-coupled manner from M1 to M4.

Fig. 2.1 Design of Conventional Dynamic Comparator

Comparator is operated in two different phases that are reset and decision phases. Within the reset phase the clock is low. The tail transistors M1 and Mtail2 are off and transistors M9 and M10 are on this might charge the nodes fp and fn to VDD. The transistors MR1 and MR2 are on when fp and fn attend vdd. The voltage at OutN and OutP nodes discharges through MR1 and MR2 transistors. Within the choice, the phase clock goes to high. The transistors Mtail1 and Mtail2 are ON and M9 and M10 are OFF. During reset phase nodes fp and fn are charged to VDD the transistors M7 and M8 are ON.

Lets consider INP is greater than INN. Within the reset phase, the nodes fp and fn are charged to VDD. Since INP is greater the node fn is discharging fastly compared to fp node. When fn goes to ground level the transistor MC1 will get ON. This makes the node fp to agitate to VDD. When fp charges to VDD the transistor MC2 will pack up this makes the node fn to discharges completely. Since fp is charged to VDD this might makes the transistor MR1 activate. The node OutN will discharges and which is connected to latch will make the OutP is charged to high.

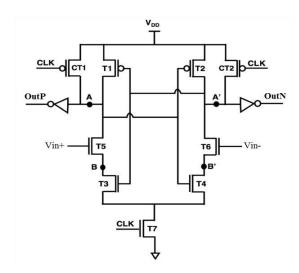

### **B.** Strong ARM Latch Comparator

Strong ARM Latch Comparator is used for medium frequency applications. It consumes zero static power and directly produces rail to rail output it means, whose dynamic range is able to reach the extremes of the supply voltage [3]. Figure 2.2 shows the Strong ARM Latch Comparator.

Fig. 2.2 Strong ARM Latch Dynamic Comparator

When the clock is low the transistors M5 to M10 are ON because of PMOStransistors. Theinternal capacitors at Nodes A, A' and B, B' are charge to VDD. The outn and outp are at zero state because its connected to inverters. When the clock goes high comparator will be activated and Mtail transistor is on.

Let INP is greater than INN, the transistor M2 is on faster than the M1 and it discharges quickly through Mtail transistor. Once the potential at B' goes to ground and it is connected to invertor circuit the outP becomes high. Since the latch is connected in above i.e cross coupled of invertors the outN becomes low when A' becomes low. (A' = B')

One of the restrictions during this topology is that the clock feedthrough problem. The voltages at A and A' follow the clock for a small period, leading to spike >VDD when the clock goes High, and another spike

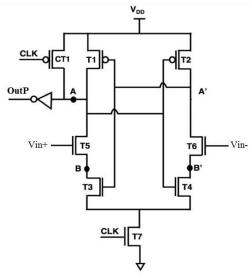

#### C. Modified Strong ARM Latch Dynamic Comparator

The below Figure 2.3 shows Modified Strong ARM Latch Comparator reduced transistor count from the original. Here the Inverting and Non-inverting transistors are placed in between latch.

Fig. 2.3 Modified Strong ARM Latch Dynamic Comparator

When clock goes low the transistors CT1 and CT2 are on. The nodes A and A' are charged to VDD. When clock goes high transistor T7 is on and comparator is on. When Vin- is greater than Vin+ , the charge at node A' discharges quickly compared to charge at A. When charge at A' goes to ground level the OutN becomes High.

Since, the comparator is designed for Flash ADC and it requires only one outputto compareboth non-inverting and inverting signals.

Hence, Fig. 2.3 can be modified as Fig. 2.4 so that the transistor count can be reduced. The transistor CT2 and invertor at outN are removed.

Fig. 2.4. Modified Strong ARM Latch Dynamic Comparator III. RESULTS AND COMPARISION

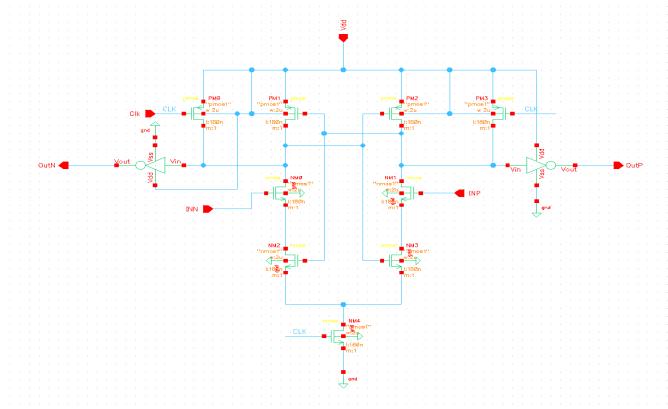

All the comparators are designed and simulated in cadence virtuoso 180nm and 45nm technologies.

Fig. 3.1. Schematic Design of Modified Strong ARM Latch Dynamic Comparator in cadence virtuoso

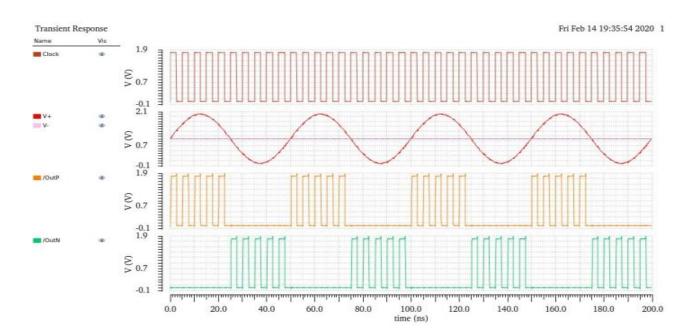

Fig. 3.2 shows the results of comparator when sinusoidal signal (2V p-p and) is given to non-inverting terminal and constant dc signal is given to inverting terminal of a comparator.

Fig. 3.2 Results of a Comparator

Tables I&II show the comparison results of all the designs and input values for the comparator.

**Table I. Comparison Results of Comparator**

|                                               | 180nm  |       | 45nm  |       |

|-----------------------------------------------|--------|-------|-------|-------|

| Comparator                                    | Power  | Delay | Power | Delay |

|                                               | (µW)   | (ns)  | (µW)  | (ns)  |

| Conventional Dynamic<br>Comparator            | 54.735 | 26.72 | 0.642 | 28.53 |

| Strong Arm Latch Comparator (15T)             | 39.97  | 25.56 | 0.308 | 26.57 |

| Modified Strong Arm Latch<br>Comparator (13T) | 32.50  | 25.53 | 0.242 | 26.54 |

**Table II. Input Values for Comparator**

|                | 180nm  | 45nm   |

|----------------|--------|--------|

| VDD            | 2V p-p | 1V p-p |

| Input Freq.    | 20Mhz  | 20Mhz  |

| Sampling Freq. | 200Mhz | 200Mhz |

#### IV. CONCLUSION

All the designed comparators are simulated in 180nm and 45nm using Cadence Virtuoso. The power of Modified Strong ARM Latch Dynamic Comparator reduced 40.6% and 18.68% compared Conventional Dynamic Comparator and Strong Arm Latch Comparator.

#### **REFERENCES**

- [1] HazratPatil, Raghavendra M, "Low Power Dynamic Comparator For 4 bit Flash ADC" 2016 IEEE International Conference on Computational Intelligence and Computing Research (ICCICR).

- [2] R. Sunil; R.K. Siddharth, Nithin Kumar Y B and Vasantha M.H, "An Asynchronous Analog to Digital Converter for Video Camera Applications," 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI).

- [3] Suman Biswas, Jitendra Kumar Das and Rajendra Prasad, "Design and Implementation of 4 Bit Flash ADC Using Low Power Low Offset Dynamic Comparator," 2015 International Conference on Electrical, Electronics, Signal, Communication and Optimization (EESCO).

- [4] N.BalaDastagiri and Dr.K.Babulu, "Clocked Low Power High Speed Regenerative Comparator," Innovations in Information, Embedded and Communication systems (ICIIECS), 2015 International Conference, 2015, pp. 1-5.

- [5] Samaneh Babayan-Mashhadi and Reza Lotfi, "Analysis and Design of Low Power Low Voltage Double tail Comparator," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol 22, No. 2, 2014, pp. 343-352.

- [6] Shabi Tabassum, Anush Bekal and Manish Goswami, "A Low Power Preamplifier Latch based comparator using 180nm CMOS Technology," 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), 2013, pp. 208-212

- [7] Raja Mohd. Noor Hafizi Raja Daud, Mamun Bin Ibne Reaz, and Labonnah Farzana Rahman, "Design and Analysis of Low Power and High Speed Dynamic Latch Comparator in 180 nm CMOS Process," International Journal of Information and Electronics Engineering, Vol. 2, No. 6, 2012, DOI: 10.7763/IJIEE.2012.V2.247

- [8] Shu, Yujun and Mei, Fengyi and Yu, Youling and Wu, Jiangfeng, "A 5-bit 500-MS/s Asynchronous Digital Slope ADC with Two Comparators," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 4, pp.426-430, April 2018.

- [9] S. R. K., S. R., N. K. Y. B., V. M. H. and E. Bonizzoni, "An Asynchronous Analog to Digital Converter for Surveillance Camera Applications," 2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Hong Kong, 2018, pp. 164-169.

- [10] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65", *IEEE Trans. Circuits Syst. II Exp. Briefs*, vol. 56, no. 11, pp. 810-814, Nov. 2009.

- [11] Y. Okaniwa, H. Tamura, M. Kibune, D. Yamazaki, T.-S. Cheung, J. Ogawa, et al., "A 40 G-b/s CMOS clocked comparator with bandwidth modulation technique", *IEEE J. Solid-State Circuits*, vol. 40, pp. 1680-1687, Aug. 2005.

- [12] P. Nuzzo, F. D. Bernardinis, P. Terreni and G. Van der Plas, "Noise analysis of regenerative comparators for reconfigurable ADC architectures", *IEEE Trans. Circuits Syst. I Reg. Papers*, vol. 55, no. 6, pp. 1441-1454, Jul. 2008.

- [13] J.M. Rabaey, "Digital Integrated Circuit Design", pg:297-302.

- [14] R. Jacob Baker, "CMOS: Mixed-Signal Circuit Design", 2nd Edition, ISBN: 978-0-470-29026-2, 1989.

- [15] D. Johns and K. Martin, Analog Integrated Circuit Design, USA, New York: Wiley, 1997.

E.Chandrasekhar is working as Assistant Professor in the department of Electronics and Communication Engineering, Chaitanya Bharathi Institute of Technology (A) from 18th July, 2012. He is pursuing his Ph.D from JNTUK, Kakinada in the area of VLSI; he did his M.E (Embedded Systems &VLSI Design) form University College of Engineering, O.U and completed did his B.Tech (ECE) form GATES Institute of Technology, JNTU. His research interest includes Analog and mixed signal IC Design. He has 12 years of experience in teaching. He has published over 10 research papers in International Journals and Conferences.

Dr. K. Ramanjaneyulu, Presently, he is working as a Professor in the Department of ECE, PVP Siddhartha Institute of Technology, Vijayawada. He is also holding a position as a chairman of IETE,Vijayawada local center. He did his B. Tech in Bapatla Engineering College during 1986-90 and then completed M. Tech in Pondicherry Engineering College in 1993. After that, he received Doctoral Degree from Andhra University in 2012. He has over 25 years of teaching experience and 10years of research experience. He has 40 publications in various Journals and Conference Proceedings. His research interests are in the areas of Digital Image Processing, Digital Image Watermarking and Wireless communications.